# X20CP1301, X20CP1381 and X20CP1382

## 1 General information

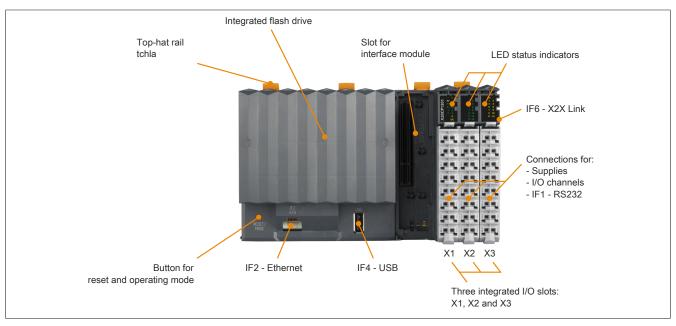

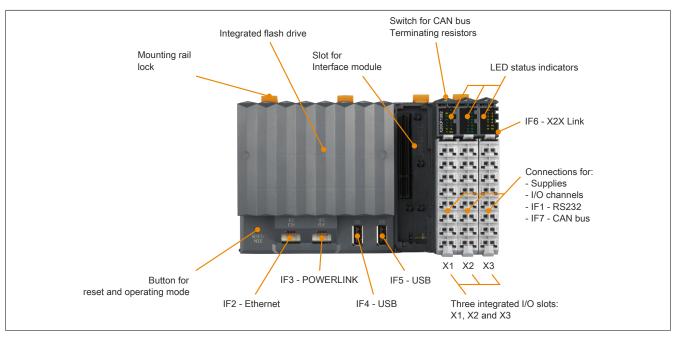

Compact CPUs are available with processor speeds of 200 MHz and 400 MHz. Depending on the variant, up to 256 MB RAM and up to 32 kB nonvolatile onboard RAM is available. A built-in flash drive is available to store up to 2 GB of application and other data.

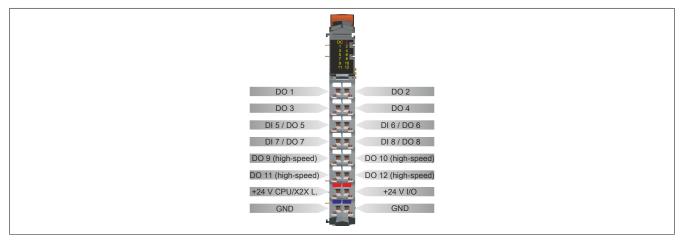

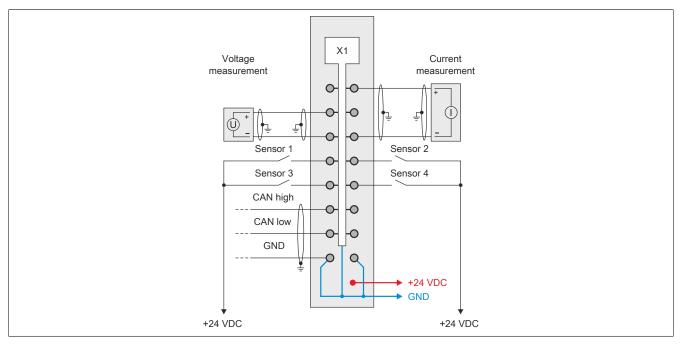

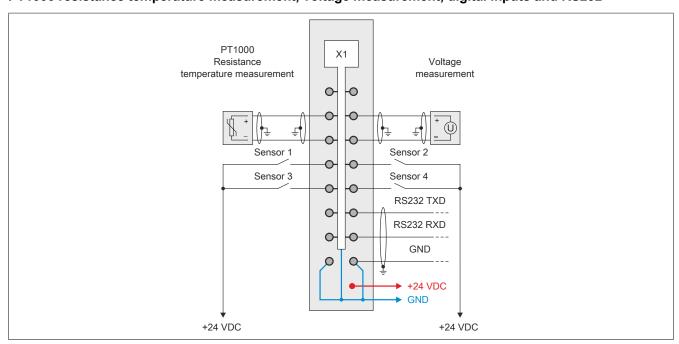

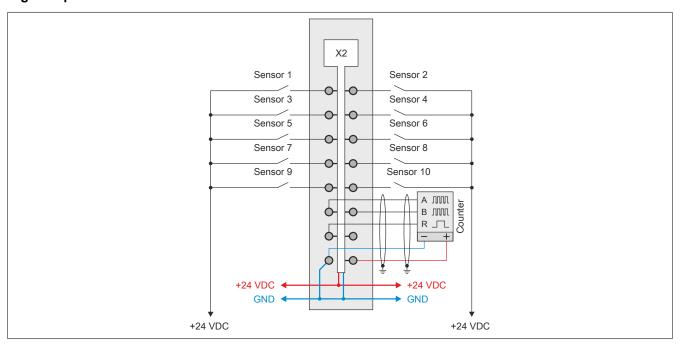

All CPUs come equipped with Ethernet, USB and one RS232 interface. In both performance classes, integrated POWERLINK and CAN bus interfaces are also available. If additional fieldbus connections are needed, all CPUs can be upgraded with an interface module from the standard X20 product range. These CPUs do not require fans or batteries and are therefore maintenance-free. 30 different digital inputs and outputs and two analog inputs are integrated in the devices. One analog input can be used for PT1000 resistance temperature measurement.

- CPU is Intel® ATOM™ 400 MHz compatible with integrated I/O processor

- Ethernet, POWERLINK with poll-response chaining and USB onboard

- 1 slot for modular interface expansion

- 30 digital inputs/outputs and two analog inputs integrated in the device

- · 1/2 GB flash drive onboard

- 128/256 MB DDR3 SDRAM

- Fanless

- No battery

- · Battery-backed real-time clock

# 2 Order data

| Model number | Short description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | X20 CPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| X20CP1301    | X20 CPU, with integrated I/O, x86-200, 128 MB DDR3 RAM, 16 kB FRAM, 1 GB flash drive onboard, 1 insert slot for X20 interface modules, 1 USB interface, 1 RS232 interface, 1 Ethernet interface 10/100 Base-T, 14 digital inputs, 24 VDC, sink, 4 digital inputs, 2 VDC, sink, 4 digital outputs, 24 VDC, 0.5 A, 5 ource, 4 digital outputs, 2 µs, 24 VDC, 0.2 A, 4 digital inputs/outputs, 24 VDC, 0.5 A, 2 analog inputs ±10 V or 0 to 20 mA / 4 to 20 mA, 1 PT1000 instead of an analog input, including power supply module, 3x X20TB1F terminal blocks, slot cover and X20 locking plate X20AC0SR1 (right) included                                                                                             |

| X20CP1381    | X20 CPU, with integrated I/O, x86-200, 128 MB DDR3 RAM, 16 kB FRAM, 2 GB flash drive on board, 1 insert slot for X20 interface modules, 2 USB interfaces, 1 RS232 interface, 1 CAN bus interface, 1 POWERLINK interface, 1 Ethernet interface 10/100 Base-T, 14 digital inputs, 24 VDC, sink, 4 digital inputs, 2 μS, 24 VDC, sink, 4 digital outputs, 24 VDC, 0.5 A, source, 4 digital outputs, 2 μS, 24 VDC, 0.2 A, 4 digital inputs/outputs, 24 VDC, 0.5 A, 2 analog inputs ±10 V or 0 to 20 mA / 4 to 20 mA, 1 PT1000 instead of an analog input, including supply module, 3x X20TB1F terminal blocks, slot cover and X20AC0SR1 locking plate (right) included                                                   |

| X20CP1382    | X20 CPU, with integrated I/O, x86-400, 256 MB DDR3 RAM, 32 kB FRAM, 2 GB flash drive on board, 2 insert slot for X20 interface modules, 2 USB interfaces, 1 RS232 interface, 1 CAN bus interface, 1 POWERLINK interface, 1 Ethernet interface 10/100 Base-T, 14 digital inputs, 24 VDC, sink, 4 digital inputs, 24 VDC, o.5 A, source, 4 digital outputs, 2 µs, 24 VDC, 0.2 A, 4 digital inputs/outputs, 24 VDC, 0.5 A, source, 4 digital outputs, 2 µs, 24 VDC, 0.2 A, 4 digital inputs/outputs, 24 VDC, 0.5 A, 2 analog inputs ±10 V or 0 to 20 mA / 4 to 20 mA, 1 PT1000 instead of an analog input, including supply module, 3x X20TB1F terminal blocks, slot cover and X20AC0SR1 locking plate (right) included |

Table 1: Order data

# **Content of delivery**

| Model number | Quantity | Short description                        |

|--------------|----------|------------------------------------------|

| -            | 1        | Interface module slot cover              |

| X20AC0SR1    | 1        | X20 locking plate, right                 |

| X20TB1F      | 3        | X20 terminal block, 16-pin, 24 VDC keyed |

Table 2: Content of delivery

# 3 Technical data

| Product ID                                                           | X20CP1301                                                                               | X20CP1381                               | X20CP1382                                                            |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------|

| Short description                                                    |                                                                                         |                                         |                                                                      |

| Interfaces                                                           | 1x RS232, 1x Ethernet,                                                                  | 1x RS232. 1x Fth                        | ernet, 1x POWER-                                                     |

| menado                                                               | 1x USB, 1x X2X Link                                                                     | ,                                       | 2X Link, 1x CAN bus                                                  |

| System module                                                        |                                                                                         | CPU                                     |                                                                      |

| General information                                                  |                                                                                         |                                         |                                                                      |

| Cooling                                                              |                                                                                         | Fanless                                 |                                                                      |

|                                                                      | 0                                                                                       |                                         | 0DADD                                                                |

| B&R ID code                                                          | 0xE35B                                                                                  | 0xE35C                                  | 0xDABB                                                               |

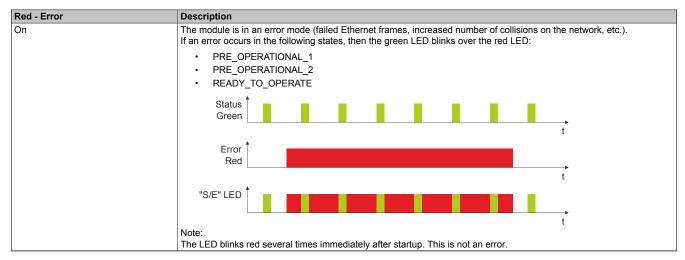

| Status indicators                                                    | CPU function, Ethernet,<br>RS232, CPU supply, I/O sup-<br>ply, I/O function per channel |                                         | LINK, RS232, CAN bus, CAN bus<br>/O supply, I/O function per channel |

| Diagnostics                                                          |                                                                                         |                                         |                                                                      |

| Outputs                                                              | Digital outputs: Ye                                                                     | es, using status LED and software (o    | output error status)                                                 |

| CPU function                                                         |                                                                                         | Yes, using status LED                   |                                                                      |

| CAN bus data transfer                                                | -                                                                                       | Yes, using                              | status LED                                                           |

| RS232 data transfer                                                  |                                                                                         | Yes, using status LED                   |                                                                      |

| Inputs                                                               | Analog                                                                                  | inputs: Yes, using status LED and s     | software                                                             |

| Ethernet                                                             |                                                                                         | Yes, using status LED                   |                                                                      |

| I/O supply                                                           |                                                                                         | Yes, using status LED                   |                                                                      |

| POWERLINK                                                            | _                                                                                       |                                         | status LED                                                           |

| Supply voltage monitoring                                            |                                                                                         | Yes, using status LED                   |                                                                      |

| Overtemperature                                                      |                                                                                         | Yes, using software                     |                                                                      |

| Terminating resistors                                                | _                                                                                       |                                         | status LED                                                           |

| CPU redundancy possible                                              |                                                                                         | No                                      |                                                                      |

| ACOPOS capability                                                    |                                                                                         | Yes                                     |                                                                      |

| . ,                                                                  |                                                                                         |                                         | -                                                                    |

| reACTION-capable I/O channels                                        |                                                                                         | No                                      |                                                                      |

| Visual Components support                                            |                                                                                         | Yes                                     |                                                                      |

| Power consumption without interface module and USB                   |                                                                                         | TBD                                     |                                                                      |

| Internal power consumption of the X2X Link and I/                    |                                                                                         |                                         |                                                                      |

| O supply 1)                                                          |                                                                                         |                                         |                                                                      |

| Bus                                                                  |                                                                                         | TBD                                     |                                                                      |

| Internal I/O                                                         |                                                                                         | TBD                                     |                                                                      |

| Additional power dissipation caused by the actuators (resistive) [W] |                                                                                         | -                                       |                                                                      |

| Electrical isolation                                                 |                                                                                         |                                         |                                                                      |

| Power supply                                                         |                                                                                         |                                         |                                                                      |

| I/O feed - I/O supply                                                |                                                                                         | No                                      |                                                                      |

| CPU/X2X Link feed - CPU/IF6                                          |                                                                                         | Yes                                     |                                                                      |

| IF1 - IF2                                                            |                                                                                         | Yes                                     |                                                                      |

| IF1 - IF3                                                            | -                                                                                       | Y                                       | es                                                                   |

| IF1 - IF4                                                            |                                                                                         | No                                      |                                                                      |

| IF1 - IF5                                                            | _                                                                                       |                                         | lo                                                                   |

| IF1 - IF6                                                            |                                                                                         | Yes                                     |                                                                      |

| IF1 - IF7                                                            | _                                                                                       | i .                                     | lo                                                                   |

| IF2 - IF3                                                            | _                                                                                       | I                                       | es                                                                   |

| IF2 - IF4                                                            |                                                                                         | Yes                                     |                                                                      |

| IF2 - IF5                                                            | _                                                                                       | i .                                     | es                                                                   |

| 1F2 - 1F3<br>  1F2 - 1F6                                             | _                                                                                       | Yes                                     |                                                                      |

| 1F2 - 1F6<br>  1F2 - 1F7                                             |                                                                                         | 1                                       | es                                                                   |

|                                                                      | _                                                                                       |                                         |                                                                      |

| IF3 - IF4                                                            | _                                                                                       |                                         | es                                                                   |

| IF3 - IF5                                                            | -                                                                                       |                                         | es                                                                   |

| IF3 - IF6                                                            | -                                                                                       |                                         | es                                                                   |

| IF3 - IF7                                                            | -                                                                                       |                                         | es                                                                   |

| IF4 - IF5                                                            | -                                                                                       | I .                                     | lo .                                                                 |

| IF4 - IF6                                                            |                                                                                         | Yes                                     |                                                                      |

| IF4 - IF7                                                            | -                                                                                       |                                         | lo                                                                   |

| IF5 - IF6                                                            | -                                                                                       | Y                                       | es                                                                   |

| IF5 - IF7                                                            | -                                                                                       |                                         | lo                                                                   |

| IF6 - IF7                                                            | -                                                                                       | Y                                       | es                                                                   |

| Channel - Bus                                                        |                                                                                         | Yes                                     |                                                                      |

| Channel - Channel                                                    |                                                                                         | No                                      |                                                                      |

| Channel - PLC                                                        |                                                                                         | No                                      |                                                                      |

| PLC - IF1 (RS232)                                                    |                                                                                         | No                                      |                                                                      |

| PLC - IF2 (Ethernet)                                                 |                                                                                         | Yes                                     |                                                                      |

| PLC - IF3 (POWERLINK)                                                | _                                                                                       | i .                                     | es                                                                   |

| PLC - IF4 (USB)                                                      |                                                                                         | l No                                    |                                                                      |

| PLC - IF 4 (USB)                                                     | _                                                                                       |                                         | lo                                                                   |

| PLC - IF6 (V2X Link)                                                 | _                                                                                       | Yes                                     |                                                                      |

| , ,                                                                  |                                                                                         | i e e e e e e e e e e e e e e e e e e e | lo.                                                                  |

| PLC - IF7 (CAN bus)                                                  | -                                                                                       | <u> </u>                                | lo<br>                                                               |

| Certification                                                        |                                                                                         |                                         |                                                                      |

| CE                                                                   |                                                                                         | Yes                                     |                                                                      |

| GOST-R                                                               |                                                                                         | Yes                                     |                                                                      |

Table 3: Technical data

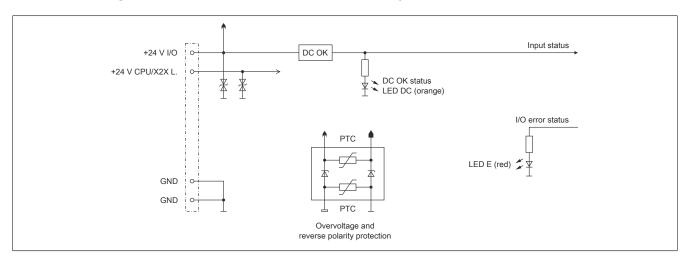

| Product ID                      | X20CP1301 X20CP1381                                              | X20CP1382                 |  |  |  |  |  |

|---------------------------------|------------------------------------------------------------------|---------------------------|--|--|--|--|--|

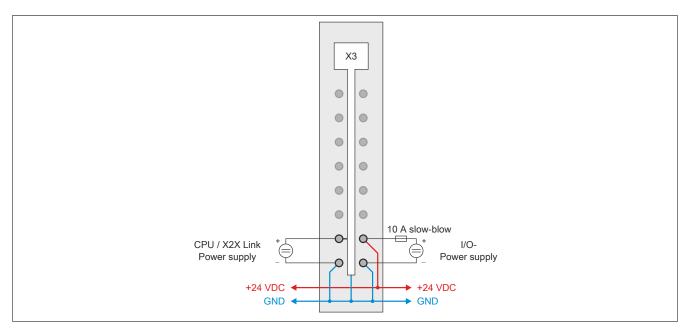

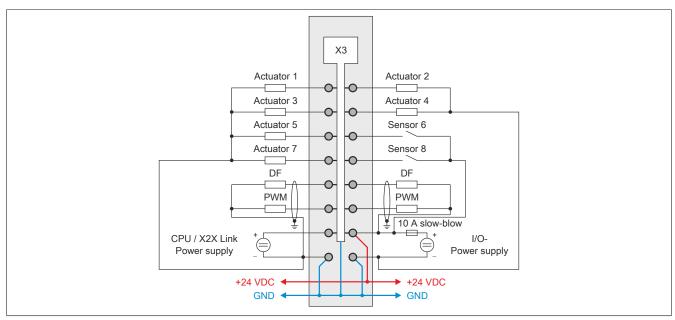

| CPU and X2X Link supply         |                                                                  |                           |  |  |  |  |  |

| Input voltage                   | 24 VDC -15% / +20%                                               |                           |  |  |  |  |  |

| Input current                   | Max. TBD A                                                       |                           |  |  |  |  |  |

| Fuse                            | Integrated, cannot be replaced                                   |                           |  |  |  |  |  |

| Reverse polarity protection     | Yes                                                              |                           |  |  |  |  |  |

| X2X Link supply output          | <u></u>                                                          |                           |  |  |  |  |  |

| Nominal output power            | 2 W                                                              |                           |  |  |  |  |  |

| Parallel operation              | Yes <sup>2)</sup>                                                |                           |  |  |  |  |  |

| Redundant operation             | Yes 3)                                                           |                           |  |  |  |  |  |

| Input I/O supply                |                                                                  |                           |  |  |  |  |  |

| Input voltage                   | 24 VDC -15% / +20%                                               |                           |  |  |  |  |  |

| Fuse                            | Required line fuse: Max. 10 A, slow-bl                           | ow                        |  |  |  |  |  |

| Output I/O supply               |                                                                  |                           |  |  |  |  |  |

| Rated output voltage            | 24 VDC                                                           |                           |  |  |  |  |  |

| Permitted contact load          | 10 A                                                             |                           |  |  |  |  |  |

| Controller                      |                                                                  |                           |  |  |  |  |  |

| Real-time clock                 | Buffering for at least 300 hours at 25°C, 1 s resolution, -18 to | 28 ppm accuracy at 25°C   |  |  |  |  |  |

| FPU                             | Yes                                                              |                           |  |  |  |  |  |

| Processor                       |                                                                  | -                         |  |  |  |  |  |

| Туре                            | Vx86EX                                                           |                           |  |  |  |  |  |

| Clock frequency                 | 200 MHz                                                          | 400 MHz                   |  |  |  |  |  |

| L1 cache                        |                                                                  | •                         |  |  |  |  |  |

| Data code                       | 16 kB                                                            |                           |  |  |  |  |  |

| Program code                    | 16 kB                                                            |                           |  |  |  |  |  |

| L2 cache                        | 128 kB                                                           |                           |  |  |  |  |  |

| Integrated I/O processor        | Processes I/O data points in the background                      | ound                      |  |  |  |  |  |

| Modular interface slots         | 1                                                                |                           |  |  |  |  |  |

| Remanent variables              | 16 kB FRAM, buffering >10 years 4)                               | 32 kB FRAM, buffer-       |  |  |  |  |  |

|                                 |                                                                  | ing >10 years 4)          |  |  |  |  |  |

| Shortest task class cycle time  | 2 ms                                                             | 1 ms                      |  |  |  |  |  |

| Typical instruction cycle time  | 0.0419 µs                                                        | 0.0199 µs                 |  |  |  |  |  |

| Standard memory                 |                                                                  |                           |  |  |  |  |  |

| RAM                             | 128 MB DDR3 SDRAM                                                | 256 MB DDR3 SDRAM         |  |  |  |  |  |

| Application memory              |                                                                  | _                         |  |  |  |  |  |

| Туре                            | 1 GB eMMC flash memory                                           | 2 GB eMMC flash memory    |  |  |  |  |  |

| Data retention                  | 10 years                                                         |                           |  |  |  |  |  |

| Writable data amount            |                                                                  |                           |  |  |  |  |  |

| Guaranteed                      | 40 TB                                                            |                           |  |  |  |  |  |

| Results for 5 years             | 21.9 GB/day                                                      |                           |  |  |  |  |  |

| Guaranteed clear/write cycles   | 20,000                                                           |                           |  |  |  |  |  |

| Error correction coding (ECC)   | Yes                                                              |                           |  |  |  |  |  |

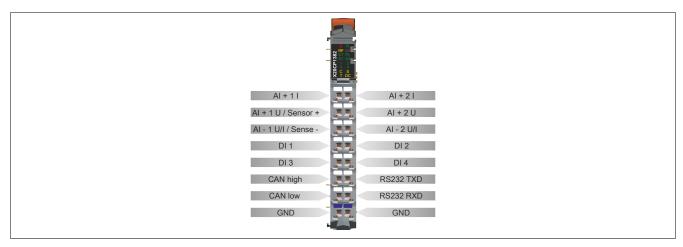

| Interfaces                      |                                                                  |                           |  |  |  |  |  |

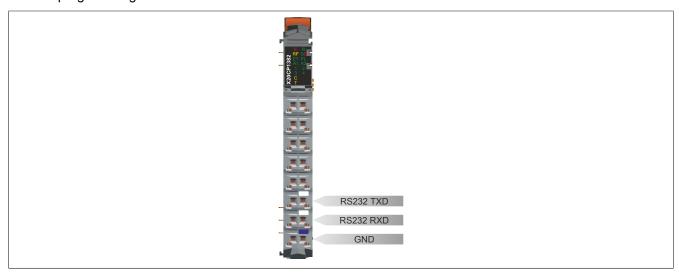

| IF1 interface                   |                                                                  |                           |  |  |  |  |  |

| Signal                          | RS232                                                            |                           |  |  |  |  |  |

| Design                          | Connection made using 16-pin X20TB1F term                        | ninal block               |  |  |  |  |  |

| Max. distance                   | 900 m                                                            |                           |  |  |  |  |  |

| Transfer rate                   | Max. 1152 kbit/s                                                 |                           |  |  |  |  |  |

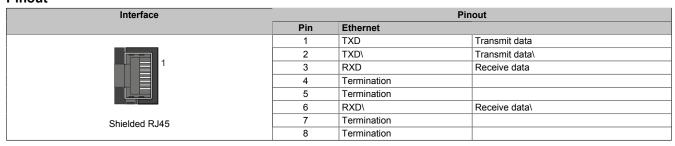

| IF2 interface                   |                                                                  |                           |  |  |  |  |  |

| Signal                          | Ethernet                                                         |                           |  |  |  |  |  |

| Design                          | 1x RJ45 shielded                                                 |                           |  |  |  |  |  |

| Cable length                    | Max. 100 m between 2 stations (segment                           | length)                   |  |  |  |  |  |

| Transfer rate                   | 10/100 Mbit/s                                                    |                           |  |  |  |  |  |

| Transmission                    | 10DACE T / 100DACE TV                                            |                           |  |  |  |  |  |

| Physical interfaces             | 10BASE-T / 100BASE-TX                                            |                           |  |  |  |  |  |

| Half-duplex                     | Yes<br>Yes                                                       |                           |  |  |  |  |  |

| Full-duplex                     | Yes                                                              |                           |  |  |  |  |  |

| Autonegotiation Auto-MDI / MDIX | Yes                                                              |                           |  |  |  |  |  |

| IF3 interface                   | 162                                                              |                           |  |  |  |  |  |

| Fieldbus                        | - POWEDLINK manag                                                | ing or controlled node    |  |  |  |  |  |

| Type                            |                                                                  | e 4 5)                    |  |  |  |  |  |

| Design                          |                                                                  | shielded                  |  |  |  |  |  |

| Cable length                    |                                                                  | stations (segment length) |  |  |  |  |  |

| Transfer rate                   |                                                                  | Mbit/s                    |  |  |  |  |  |

| Transmission                    |                                                                  | <del>-</del>              |  |  |  |  |  |

| Physical interfaces             | -   100BA                                                        | ASE-TX                    |  |  |  |  |  |

| Half-duplex                     |                                                                  | es                        |  |  |  |  |  |

| Full-duplex                     |                                                                  | 10                        |  |  |  |  |  |

| Autonegotiation                 |                                                                  | es                        |  |  |  |  |  |

| Auto-MDI / MDIX                 | I                                                                | es                        |  |  |  |  |  |

| IF4 interface                   |                                                                  |                           |  |  |  |  |  |

| Type                            | USB 1.1/2.0                                                      |                           |  |  |  |  |  |

| Design                          | Type A                                                           |                           |  |  |  |  |  |

| Max. output current             | 0.5 A                                                            |                           |  |  |  |  |  |

| 1 1 1 1                         |                                                                  |                           |  |  |  |  |  |

Table 3: Technical data

| Product ID                                              | X20CP1301                      | X20CP1381                                                                                       | X20CP1382                     |  |

|---------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|--|

| IF5 interface                                           | AZUCPTSUT                      | A200P1301                                                                                       | A200P130Z                     |  |

| Type                                                    | _                              | USB 1.                                                                                          | 1/2 0                         |  |

| Design                                                  | _                              | Туре                                                                                            |                               |  |

| Max. output current                                     | _                              | 0.1                                                                                             |                               |  |

| IF6 interface                                           |                                |                                                                                                 |                               |  |

| Fieldbus                                                |                                | X2X Link master                                                                                 |                               |  |

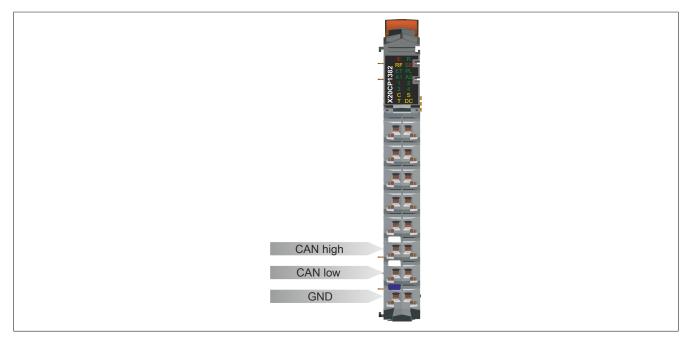

| IF7 interface                                           |                                |                                                                                                 |                               |  |

| Signal                                                  | -                              | CAN                                                                                             | bus                           |  |

| Design                                                  | -                              | Connection made using 16-p                                                                      | oin X20TB1F terminal block    |  |

| Max. distance                                           | -                              | 1000                                                                                            |                               |  |

| Transfer rate                                           | -                              | Max. 1                                                                                          | =                             |  |

| Terminating resistors                                   | -                              | Integrated in                                                                                   |                               |  |

| Controller                                              | -                              | SJA 1                                                                                           | 1000                          |  |

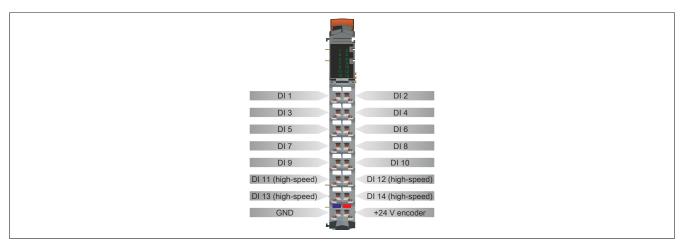

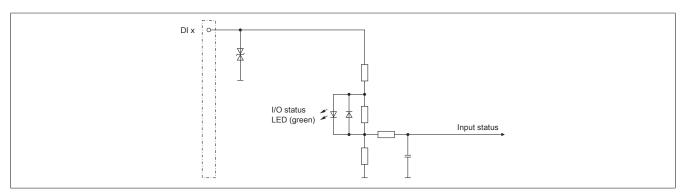

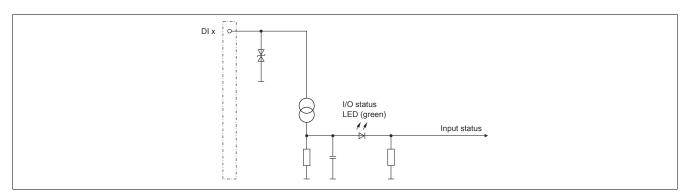

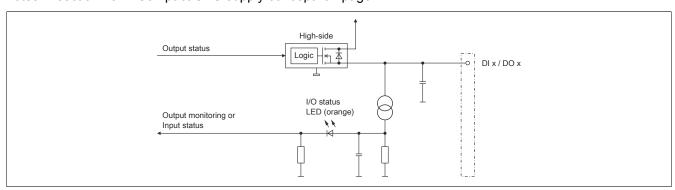

| Digital inputs                                          |                                |                                                                                                 |                               |  |

| Quantity                                                |                                | d inputs, 4 high-speed inputs and 4 m                                                           |                               |  |

| Naminal valtage                                         | neis, cor                      | figurable as inputs or outputs using s                                                          | Boilware                      |  |

| Nominal voltage                                         |                                | 24 VDC -15% / +20%                                                                              |                               |  |

| Input voltage Input current at 24 VDC                   |                                | X1 - Standard inputs: Typ. 3.5 mA                                                               |                               |  |

| Imput current at 24 VDC                                 |                                | X2 - Standard inputs: Typ. 3.5 mA                                                               |                               |  |

|                                                         |                                | X2 - High-speed inputs: Typ. 3.5 mA                                                             |                               |  |

|                                                         |                                | X3 - Mixed channels: Typ. 2.68 mA                                                               |                               |  |

| Input filter                                            |                                |                                                                                                 |                               |  |

| Hardware                                                |                                | dard inputs and mixed channels: ≤20                                                             |                               |  |

|                                                         | , , ,                          | outs: ≤2 µs, when used as standard in                                                           |                               |  |

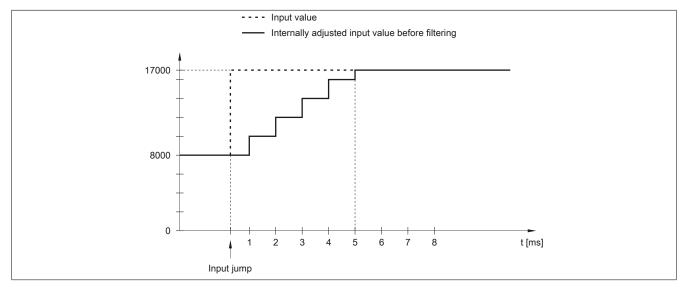

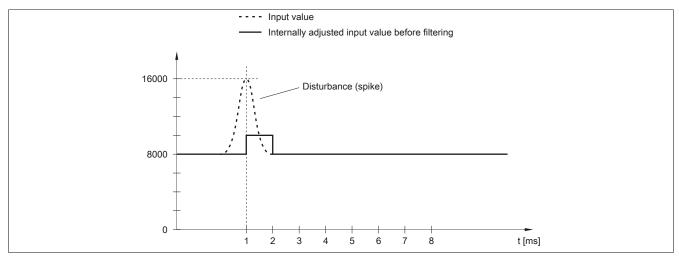

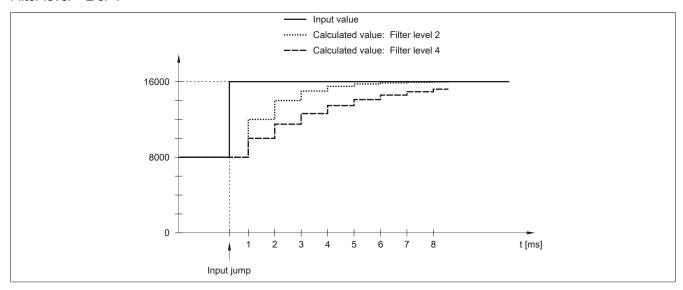

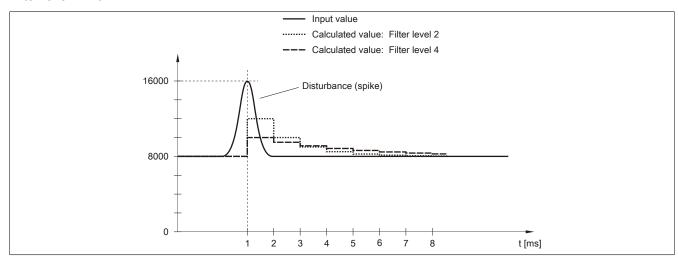

| Software                                                | Default 1 ms, co               | onfigurable between 0 and 25 ms in 0                                                            | 0.1 ms intervals              |  |

| Connection type                                         |                                | 1-wire connections                                                                              |                               |  |

| Input circuit                                           |                                | Sink                                                                                            |                               |  |

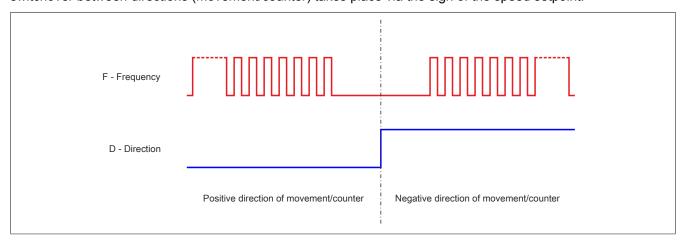

| Additional functions                                    |                                | X2 - High-speed digital inputs:                                                                 |                               |  |

|                                                         |                                | <ul> <li>AB counter, ABR incremental encoor<br/>rement, differential time measuremer</li> </ul> |                               |  |

| Input resistance                                        | od measurement, gate measu     | X1 - Standard inputs: 6.8 kΩ                                                                    | it, edge counters, edge times |  |

| input resistance                                        |                                | X2 - Standard inputs: 8.9 kΩ                                                                    |                               |  |

|                                                         |                                | X2 - High-speed inputs: 6.8 kΩ                                                                  |                               |  |

|                                                         |                                | X3 - Mixed channels: 8.9 kΩ                                                                     |                               |  |

| Switching threshold                                     |                                |                                                                                                 |                               |  |

| Low                                                     |                                | <5 VDC                                                                                          |                               |  |

| High                                                    |                                | >15 VDC                                                                                         |                               |  |

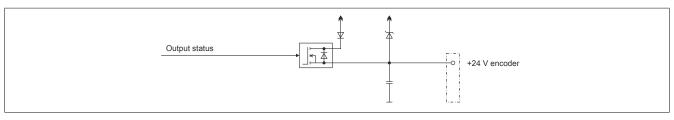

| AB incremental encoder                                  |                                |                                                                                                 |                               |  |

| Quantity                                                |                                | 2                                                                                               |                               |  |

| Encoder inputs                                          | 24 V, asymmetrical             |                                                                                                 |                               |  |

| Counter size                                            | 32-bit                         |                                                                                                 |                               |  |

| Input frequency                                         |                                | Max. 100 kHz                                                                                    |                               |  |

| Evaluation                                              |                                | 4x                                                                                              |                               |  |

| Encoder supply                                          |                                | Module-internal, max. 300 mA                                                                    |                               |  |

| Overload behavior of the encoder supply                 | Sho                            | ort circuit protection, overload protecti                                                       | ion                           |  |

| ABR incremental encoder                                 |                                |                                                                                                 |                               |  |

| Quantity                                                |                                | 1                                                                                               |                               |  |

| Encoder inputs  Counter size                            | -                              | 24 V, asymmetrical<br>32-bit                                                                    |                               |  |

|                                                         |                                |                                                                                                 |                               |  |

| Input frequency                                         | -                              | Max. 100 kHz                                                                                    |                               |  |

| Evaluation Encoder supply                               |                                | Module-internal, max. 300 mA                                                                    |                               |  |

| Encoder supply  Overload behavior of the encoder supply | Ch.                            | ort circuit protection, overload protecti                                                       | ion                           |  |

| Event counter                                           | Sno                            | or circuit protection, overload protecti                                                        |                               |  |

| Quantity                                                |                                | 2                                                                                               |                               |  |

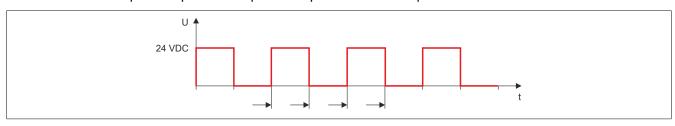

| Signal form                                             | +                              | Square wave pulse                                                                               |                               |  |

| Evaluation                                              |                                | 1x                                                                                              |                               |  |

| Input frequency                                         | +                              | Max. 250 kHz                                                                                    |                               |  |

| Counter frequency                                       | +                              | 250 kHz                                                                                         |                               |  |

| Counter riequency  Counter size                         | -                              | 32-bit                                                                                          |                               |  |

| Time measurement                                        |                                | JZ-DIL                                                                                          |                               |  |

| Possible measurements                                   | Period measurement date mos    | surement, differential time measuren                                                            | nent edge counter edge times  |  |

| Measurements per module                                 | T Chou measurement, gate files | Each function up to 4x                                                                          | non, cage counter, eage times |  |

| Counter size                                            |                                | 32-bit                                                                                          |                               |  |

| Timestamp                                               | +                              | 1 µs resolution                                                                                 |                               |  |

| Signal form                                             | +                              | Square wave pulse                                                                               |                               |  |

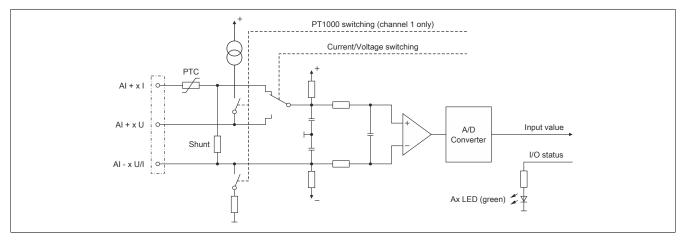

| Analog inputs                                           |                                | Oquale wave pulse                                                                               |                               |  |

| Quantity                                                |                                | 2 6)                                                                                            |                               |  |

| Input                                                   | +10 \/ or 0 to 20              | mA / 4 to 20 mA, via different termin                                                           | nal connections               |  |

| Input type                                              | 110 V 01 0 10 20               | Differential input                                                                              | 351110000110                  |  |

| Digital converter resolution                            | <u> </u>                       | Dinerential input                                                                               |                               |  |

| Voltage                                                 | 1                              | ±12-bit                                                                                         |                               |  |

| Current                                                 |                                | 12-bit                                                                                          |                               |  |

|                                                         |                                | 12 010                                                                                          |                               |  |

Table 3: Technical data

| Product ID                                          | X20CP1301 X20CP1381 X20CP1382                                                          |

|-----------------------------------------------------|----------------------------------------------------------------------------------------|

| Conversion time                                     | 1 channel enabled: 100 μs                                                              |

|                                                     | 2 channels enabled: 200 µs                                                             |

| Output format                                       |                                                                                        |

| Data type                                           | INT                                                                                    |

| Voltage                                             | INT $0x8001 - 0x7FFF / 1 LSB = 0x0008 = 2.441 \text{ mV}$                              |

| Current                                             | INT 0x0 <u>000 - 0x7FFF / 1 LSB = 0x0008 = 4.883</u> μA                                |

| Input impedance in signal range                     |                                                                                        |

| Voltage                                             | 20 ΜΩ                                                                                  |

| Current                                             | <u> </u>                                                                               |

| Load                                                |                                                                                        |

| Voltage                                             | -                                                                                      |

| Current                                             | <300 Ω                                                                                 |

| Input protection                                    | TBD: Protection against wiring with supply voltage                                     |

| Permitted input signal                              |                                                                                        |

| Voltage                                             | Max. ±30 V                                                                             |

| Current                                             | Max. ±50 mA                                                                            |

| Output of the digital value during overload         | Configurable                                                                           |

| Conversion procedure                                | SAR                                                                                    |

| Input filter                                        | 3rd-order low pass / cutoff frequency 1 kHz                                            |

| Max. error at 25°C                                  |                                                                                        |

| Voltage                                             | <u> </u>                                                                               |

| Gain                                                | 0.18% (Rev. <c0: 0.37%)="" <sup="">7)</c0:>                                            |

| Offset                                              | 0.04% (Rev. <c0: 0.25%)="" 8)<="" td=""></c0:>                                         |

| Current                                             | 04-00-44-0450//D                                                                       |

| Gain                                                | 0 to 20 mA = 0.15% (Rev. <c0: 0.52%)="" 20="" 4="" <sup="" ma="0.25%" to="">7</c0:>    |

| Offset May paid drift                               | 0 to 20 mA = 0.1% (Rev. <c0: 0.4%)="" 20="" 4="" <sup="" ma="0.15%" to="">9)</c0:>     |

| Max. gain drift                                     | 0.047.0/100.7\                                                                         |

| Voltage                                             | 0.017 %/°C <sup>7)</sup>                                                               |

| Current                                             | 0 to 20 mA = 0.015 %/°C / 4 to 20 mA = 0.023 %/°C <sup>7)</sup>                        |

| Max. offset drift                                   | 0.000 0/ (00.0)                                                                        |

| Voltage                                             | 0.008 %/°C 8)                                                                          |

| Current                                             | 0 to 20 mA = 0.008 %/°C / 4 to 20 mA = 0.012 %/°C 9)                                   |

| Common-mode rejection                               | 70 dD                                                                                  |

| DC                                                  | 70 dB                                                                                  |

| 50 Hz                                               | 70 dB                                                                                  |

| Common-mode range                                   | ±12 V                                                                                  |

| Crosstalk between channels                          | <-70 dB                                                                                |

| Non-linearity                                       | 40.005.0/.9\                                                                           |

| Voltage<br>Current                                  | <0.025 % <sup>8)</sup> <0.05 % <sup>9)</sup>                                           |

|                                                     |                                                                                        |

| Temperature inputs resistance measurement  Quantity |                                                                                        |

| Input                                               | Resistance measurement with constant current supply for 2-wire connections             |

| -                                                   | ,                                                                                      |

| Digital converter resolution                        | 13-bit                                                                                 |

| Conversion time                                     | Only temperature input enabled: 200 μs<br>Temperature and analog input enabled: 400 μs |

| Conversion procedure                                | SAR                                                                                    |

| Output format                                       | INT or UINT for resistance measurement                                                 |

| ·                                                   | IIVI OI OIIVI IOI IESISIAIICE IIIEASUIEIIIE                                            |

| Sensor<br>PT1000                                    | -200 to 850°C                                                                          |

| Resistance measurement range                        | -200 to 650 C<br>01 to 4000 Ω                                                          |

| Temperature sensor resolution                       | TBD: 1 LSB = 0.16°C                                                                    |

| Resistance measurement resolution                   | TBD: 1 LSB = 0.16 C                                                                    |

|                                                     |                                                                                        |

| Input filter                                        | 1st-order low pass / cutoff frequency 7 Hz IEC/EN 60751                                |

| Sensor standard                                     | 1 V                                                                                    |

| Common-mode range                                   |                                                                                        |

| Linearization method                                | Internal                                                                               |

| Measuring current                                   | 1 mA                                                                                   |

| Permitted input signal                              | Short-term max. ±30 V                                                                  |

| Max. error at 25°C                                  | 0.00/ /D                                                                               |

| Gain                                                | 0.3% (Rev. <c0: 1.93%)="" <sup="">10</c0:>                                             |

| Offset                                              | 0.15% (Rev. <c0: 0.32%)="" <sup="">11)</c0:>                                           |

| Max. gain drift                                     | 0.023 %/°C <sup>10)</sup>                                                              |

| Max. offset drift                                   | 0.012 %/°C ¹¹)                                                                         |

| Non-linearity                                       | <0.05 % 11)                                                                            |

| Standardized value range for resistance measure-    | 01 Ω to 40,000 Ω                                                                       |

| ment                                                | .70.10                                                                                 |

| Crosstalk between channels                          | <-70 dB                                                                                |

| Common-mode rejection                               | . 00 /D                                                                                |

| 50 Hz                                               | >60 dB                                                                                 |

| DC                                                  | TBD                                                                                    |

| Temperature sensor standardization                  | 222 - 27222                                                                            |

| PT1000                                              | -200 to 850°C                                                                          |

Table 3: Technical data

| Product ID                                          | X20CP1301 X20CP138 <sup>2</sup>                                                                               | 1 X20CP1382                                               |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

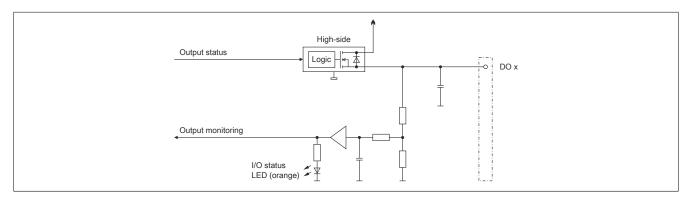

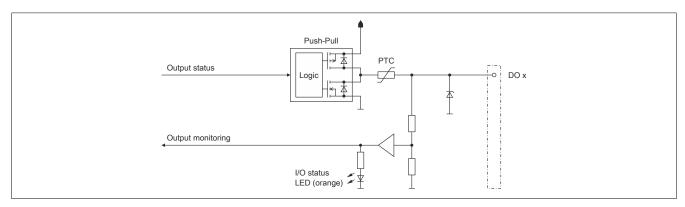

| Digital outputs                                     |                                                                                                               | ,                                                         |

| Design                                              | Standard outputs and mixed channe                                                                             | els: FET positive switching                               |

|                                                     | High-speed outputs:                                                                                           |                                                           |

| Quantity                                            | 4 standard outputs, 4 high-speed ou                                                                           | utputs and 4 mixed chan-                                  |

|                                                     | nels, configurable as inputs or o                                                                             | utputs using software                                     |

| Nominal voltage                                     | 24 VDC                                                                                                        |                                                           |

| Switching voltage                                   | 24 VDC -15% / -                                                                                               | +20%                                                      |

| Nominal output current                              | Standard outputs and mixed                                                                                    |                                                           |

| Nonmai output current                               | High-speed output                                                                                             |                                                           |

| Total nominal current                               | Standard outputs and mixe                                                                                     |                                                           |

| Total Hominal Garrent                               | High-speed output                                                                                             |                                                           |

| Connection type                                     | 1-wire connect                                                                                                |                                                           |

|                                                     | Standard outputs and mixed                                                                                    |                                                           |

| Output circuit                                      | Standard outputs and mixed<br>High-speed outputs: Si                                                          |                                                           |

| Outrot and ation 12)                                |                                                                                                               |                                                           |

| Output protection 12)                               | Thermal cutoff if overcurrent or short circuit occurs<br>Internal inverse diode for switching inductive loads |                                                           |

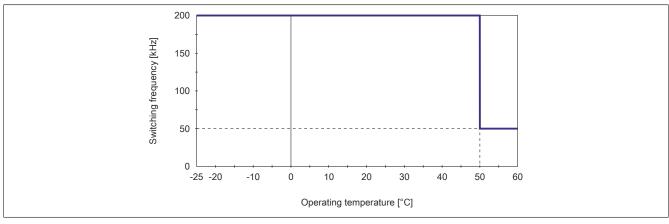

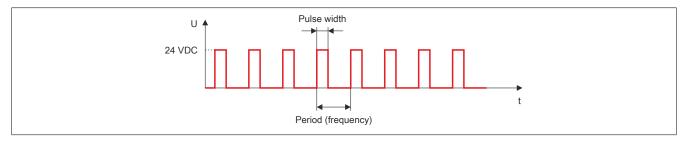

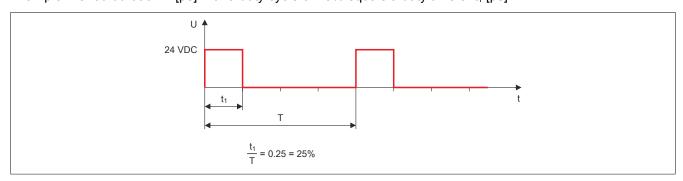

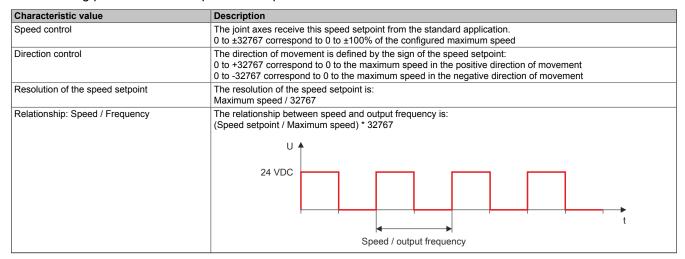

| Pulse width modulation <sup>13)</sup>               | internal inverse diode for switching inductive loads                                                          | (See Section Switching inductive loads )                  |

|                                                     | E to GEE2E up corresponde to                                                                                  | 200 kH = to 15 H=                                         |

| Period duration                                     | 5 to 65535 µs corresponds to                                                                                  |                                                           |

| Pulse duration                                      | 0.0 to 100.0%, minim                                                                                          | ·                                                         |

| Resolution for pulse duration                       | 0.1% of the configured                                                                                        |                                                           |

| Diagnostic status                                   | Standard outputs and mixed channels: Out                                                                      | tput monitoring with 10 ms delay                          |

|                                                     | High-speed outputs: Output moni                                                                               |                                                           |

| Leakage current when switched off                   | Standard outputs and mixed                                                                                    |                                                           |

|                                                     | High-speed outputs                                                                                            |                                                           |

| R <sub>DS(on)</sub>                                 | 140 mΩ <sup>14)</sup>                                                                                         |                                                           |

| Residual voltage                                    | Standard outputs and mixed channels:                                                                          | <0.1 V at 0.5 A rated current                             |

| -                                                   | High-speed outputs: <0.9 V at                                                                                 | 0.1 A rated current                                       |

| Peak short circuit current                          | Standard outputs and mixed                                                                                    | d channels: <3 A                                          |

|                                                     | High-speed outputs                                                                                            | s: <20 A                                                  |

| Switching on after overload or short circuit cutoff | Standard outputs and mixed channels: Approx. 10 r                                                             | ms (depends on the module temperature)                    |

| g                                                   | High-speed output                                                                                             |                                                           |

| Switching delay                                     |                                                                                                               |                                                           |

| 0 -> 1                                              | Standard outputs and mixed                                                                                    | channels: <300 us                                         |

|                                                     | High-speed output                                                                                             |                                                           |

| 1 -> 0                                              | Standard outputs and mixed                                                                                    | ·                                                         |

|                                                     | High-speed output                                                                                             | •                                                         |

| Switching frequency                                 |                                                                                                               |                                                           |

| Resistive load 15)                                  | Standard outputs and mixed ch                                                                                 | annels: Max 500 Hz                                        |

| recolouve load                                      | High-speed outputs: 50 kHz, max                                                                               |                                                           |

|                                                     | "Switching frequency derating for high                                                                        |                                                           |

| Inductive load                                      | See section "Switching in                                                                                     |                                                           |

| Braking voltage when switching off inductive loads  | Standard outputs and mixed ch                                                                                 | -                                                         |

| Operating conditions                                | Otandara outputs and mixed on                                                                                 | аппсю. тур. 40 400                                        |

| <u> </u>                                            |                                                                                                               |                                                           |

| Mounting orientation                                | Week                                                                                                          |                                                           |

| Horizontal                                          | Yes                                                                                                           |                                                           |

| Vertical                                            | Yes                                                                                                           |                                                           |

| Installation at elevations above sea level          |                                                                                                               |                                                           |

| 0 to 2000 m                                         | No limitation                                                                                                 |                                                           |

| >2000 m                                             | Reduction of ambient temperature                                                                              | re by 0.5°C per 100 m                                     |

| EN 60529 protection                                 | IP20                                                                                                          |                                                           |

| Environmental conditions                            |                                                                                                               |                                                           |